# **†**IJESRT

## INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

## **REVIEW PAPER ON PSEUDO-DIFFERENTIAL AND BULK-DRIVEN MOS**

**TRANSISTOR TECHNIQUE FOR OTA** Shainda J. Tahseen<sup>\*1</sup>, Sandeep Singh<sup>2</sup>

\*School of Engineering and Technology, Sharda University, Greater Noida, India

#### **DOI**: 10.5281/zenodo.829785

#### ABSTRACT

This paper presents review on Pseudo-Differential amplifier technique and Bulk-Driven MOS transistor technique for ultra-low voltage and power. By using this technique, a different design of operational transconductance amplifier (OTA) is briefly explained along with their outputs and their application. By using a pseudo-differential technique a voltage drop across the tail current is avoid as the tail-current is removed in Pseudo-differential amplifier where as by using the Bulk-Driven MOS transistor a minimum supply voltage is achieved because of the possibility in reduction of threshold voltage.

**KEYWORDS:** Pseudo-differential amplifier, Bulk-Driven MOS transistor, threshold voltage, Operational Transconductance Amplifier

#### **INTRODUCTION**

The increasing demand of low power supply as well as low power consumption circuits and system emerges the importance of operational transconductance amplifier (OTA) in analog circuits. Since, then OTA has become one of the most important building block of an analog circuits due to its several advantages.

It is an imperative for OTA to satisfy many design requirements. As the CMOS technologies develop well into the ultra-deep-sub micrometer reign, the supply voltage fall and device characteristic worsen. These fettle shew severe callout in amplifier design [1], to overcome these problem a OTA is designed by using different technique.

A pseudo differential amplifier is design instead of fully differential amplifier by removing the tail current source, by doing this the minimum supply voltage is reduced but the input common-mode range and output voltage swing are improved.

Another technique is Bulk-driven technique. Because a conventional amplifier need power supply voltage minimum to the magnitude of the PMOS or the NMOS transistor along with essential signal swing [2], as the scaling of the power supply voltages and in the reduction of the threshold voltage (Vt) in the deep sub-micron CMOS processes is not that effective over the years [3].

A different design techniques has been developed over the years without employing expensive low Vt transistors, such designs are floating –gate MOSFETs, sub-threshold design, bulk-driven MOSFETs, and level-shifting techniques. Among all these design the bulk-driven technique is the most effective and promising technique since it allows a large signal swing without cutting off the transistor [4].

This paper discusses both the design technique of OTA. Each design have their advantages that helps in obtaining ultra-low voltage and rail-to-rail input without effecting the area. This paper is organized as follow: section2 describes both the techniques individually, section 3 discusses the different OTA design realizing these techniques., section 4 discusses the conclusion.

#### **TECHNIQUES**

#### **Pseudo-Differential Amplifier**

The pseudo differential architecture is basically used to reduce the required supply voltage.Pseudo Differential is based on two independent inverters without the tail current source. It has been seen that by shunning the voltage drop across the tail-current source, it allows extensively wide input and output ranges and thus get an attention for low power supply applications.[5]

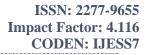

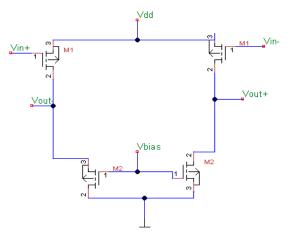

By removing the VD*sat* constraint of the tail current source, the minimum supply voltage is decreased but it results in the increment in input common-mode range and the output voltage swing. The main detract of this circuit is the serious deterioration in common-mode and power-supply rejection.[6] This is detract is shown when using the conventional pseudo-differential pair i.e without CMFF shown in fig. 1(b). To ameliorate this deterioration a common-mode feed forward (CMFF) circuit is used. Shown in fig 1(b)

Fig 1(a) Pseudo-differential pair without CMFF[7]

Fig 1(b) Pseudo-differential pair with CMFF[7]

Nevertheless Pseudo differential structutres requires an additional common-mode feedback (CMFB) circuit which serves two purposes-[5]

- 1. To affix the common-mode voltage at high impedance node.

- 2. To subdue the common-mode signal component.

http://www.ijesrt.com

## ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

#### **Bulk-Driven MOS Transistor**

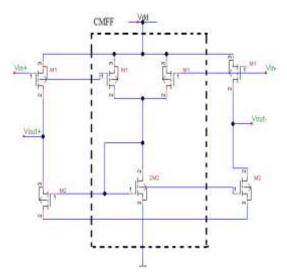

Bulk-Driven MOS transistor technique is generally used for low voltage analog circuits [7]. The operation principle of Bulk-driven MOS is alike to the JFET. It can be considered as a good solution to subside the threshold voltage. The operation principle of this technique that the value of gate-to-source voltage should be able to form an inversion layer, and an input signal is applied to the bulk terminal. By doing this the reduction in threshold voltage of a MOSFET can be achieved and can possibly be removed from the signal path. The circuit and the cross-section of bulk-driven transistor is shown in the Fig. 2.

Fig 2 Bulk-driven transistor circuit[7]

The bulk-driven transistor is work as depletion type device that operates with the zero, negative and slightly positive bias voltage. As a result, the bulk-driven technique allows the minimum voltage to be applied at the input terminal and rail-to-rail input is achieved.[6]

Despite the deduction of the threshold requirement, the bulk-driven approach suffers some drawbacks on comparing to its gate-driven counterparts. First, this approach gives the reduced speed and bandwidth because the transitional frequency of the bulk-driven transistor is lower than that of a gate-driven transistor. Second, the noise performance of this approach is worse as compared to the gate-driven transistor.

#### **OTA REALIZATION BY THESE TECHNIQUES**

#### By Pseudo differential technique

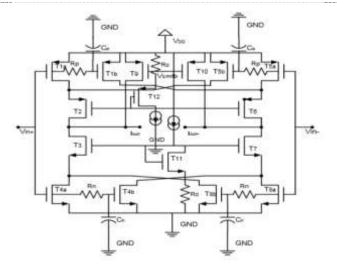

By using this technique a low voltage, low power linear pseudo differential OTA for Ultra-High frequency applications is proposed in the fig. 3

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

Fig. 3 Proposed pseudo differential OTA[8]

The proposed OTA is used to design a 9th order 400 MHz chebyshev I low-pass filter by using  $0.13 \mu m$  technology. This filter has an attenuation of 30 dB at 600 MHz and it consumes only 13mW.

A low voltage, large transconductance and linear pseudo differential OTA is proposed for ultra-high frequency design. It has been shown that by using the simple linearity improvement method, an improvement in the linearity can be achieved.

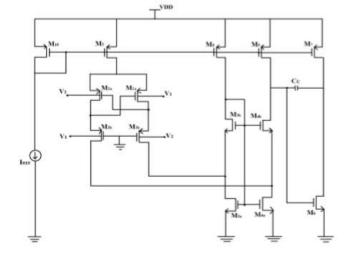

#### OTA by Bulk-Driven Technique

The low voltage OTA using bulk-driven input differential pair is designed in proposed OTA shown in fig. 4 the transistors are working in weak inversion. The circuit is simulated in 90-nm standard CMOS process in Cadence EDA software. To enhance the transconductance and the slew rate, source degeneration with the positive feedback in a differential pair methodology is used.

The proposed OTA gives the DC gain of 26 dB, gain band-width product of 750MHz, slew rate of 3.7 V/ $\mu$ s and power dissipation of 250  $\mu$ W. [9]

This OTA can be employed in low-power Bio-medical and sensors application

Fig. 4 circuit diagram of proposed OTA[9]

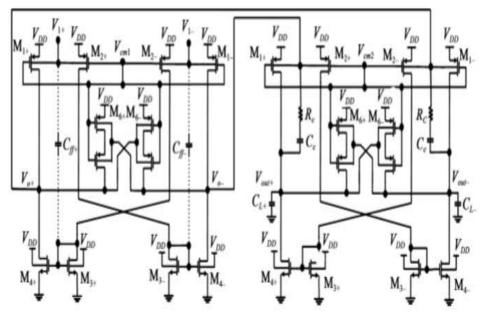

## OTA Using Both the Technique Pseudo-Differential and Bulk-Driven MOS transistor Technique

A two-stage bulk-input pseudo-differential operational transconductance amplifier (OTA) is designed in the proposed circuit [10] .This OTA was designed in 90 nm CMOS process and operates at supply voltage of 0.5 V shown in fig. 5. The DC gain and the speed of the OTA is increased by using a two-path bulk-driven OTA with the combination of two different amplifiers. By using Bulk-terminal as an input , a rail-to-rail input become possible. This OTA gives the DC gain of 70.2 dB with 2.5MHz of Gain Band-width Product along with 70.8° phase margin. This OTA has wide application in active-RC filters.

Fig 5. Two-stage bulk-input pseudo-differential OTA [10]

#### CONCLUSION

A two different design techniques for ultra low-power and voltage is explained in this paper. By using a pseudodifferential technique a voltage drop across the tail current is avoid as the tail current is removed in pseudodifferential amplifier. And to lowering threshold voltage a Bulk-Driven MOS transistor technique is used. The different OTA design by using these technique is also discussed in this paper.

#### REFERENCES

- [1] T. H. Lin, C. K Wu, and M.-C. Tsai, "A 0.8-V 0.25-mW current mirror OTA with 160-MHz GBW in 0.18- CMOS," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 2, pp.131–135, Feb.2007

- [2] B. J. Blalock, P. E. Allen and G. A.Rincon-Mora "Designing 1-V opamp using standard digital CMOS technology", IEEE Trans. Circuits sys. II Analog Digital Signal Process, vol. 45 no.7, pp. 769-780 Jul 1998.

- [3] L. Zuo, and S. K. Islam, "Low-Voltage bulk-driven operational amplifier with improved transconductance" IEEE Trans. On Circuits and Sys., regular papers vol 60, no 08, Aug 2013.

- [4] Luis h. C. Ferreira, T. C. Pimento and Robson L. Moreno, "An Ultra Low Voltage Ultra Low Power Cmos Miller Ota With Rail-To-Rail Inoput/Output Swing", IEEE Trans. Circuits and Sys. Vol 54, no. 10, Oct 2007.

- [5] A. Suadet and V. Kasemsuawam, "A 1 Volt CMOS Pseudo Differential Amplifier" Department of Electronics, Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang, Ladkrabang Dist., Bangkok, 10520, Thailand, Conference Paper December 2006.

- [6] O. Abdel fattah, G. W. Roberts, Ishiang Shih, and Yi-Chi Shih, "An Ultra-Low-Voltage CMOS Process-Insensitive Self-Biased OTAWith Rail-to-Rail InputRange," IEEE Trans. Circuits and sys., I:regular paper.,vol.62, no.10 october 2015

http://www.ijesrt.com

## [Tahseen\* et al., 6(7): July, 2017]

ICTM Value: 3.00

#### ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

- [7] S. Sing and P. Goyal, "An Ultra Low-Voltage CMOS Self-Biased OTA", International Journal of Computer Networks and Wireless Communications (IJCNWC), ISSN: 2250-3501 Vol.6, No 3, May-June 2016.

- [8] A. Kavala, Kondekar P. N, and Yang Sun, "A Low Voltage, Low Power Linear Pseudo Differential OTA for Ultra-High Frequency Applications" School of Engineering, Information and Communications University (ICU), Daejeon, Republic of Korea, DOI: 10.1109/IWAT.2009.4906929, Mar 2009.

- [9] S. Bhat, S. Choudhary and J. Selvakumar, "Design of Low Voltage CMOS OTA Using Bulk-Driven Technique" Indian Journal of Science and Technology, Vol 9(19), DOI: 10.17485/ijst/2016/v9i19/89072, May 2016.

- [10] Arash Ahmadpour. "An Ultra Low-Voltage and Low-Power OTA Using Bulk-Input Technique and Its Application in Active-RC Filters", Circuits and Systems, 2011, 2, 183-189 doi:10.4236/cs.2011.23026 Published Online July 2011 (http://www.SciRP.org/journal/cs)

## **CITE AN ARTICLE**

Tahseen, Shainda J., and Sandeep Singh. "REVIEW PAPER ON PSEUDO-DIFFERENTIAL AND BULK-DRIVEN MOS TRANSISTOR TECHNIQUE FOR OTA ." *INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY* 6.7 (2017): 596-601. Web. 15 July 2017.